## Performance Analysis with the IBM Full-System Simulator

Modeling the Performance of the Cell Broadband Engine Processor

© International Business Machines Corporation

#### Performance Analysis with the IBM Full-System Simulator

#### © International Business Machines Corporation (2007). All Rights Reserved.

Printed in the United States of America September 2007.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without prior written permission of IBM Corporation. No other rights under copyright are granted without prior written permission of IBM Corporation.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made. All information contained in this document is subject to change without notice. This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice, and is provided without warranty of any kind. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary. The document is not intended for production.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

U.S. Government Users Restricted Rights–Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corporation.

IBM is a registered trademark of International Business Machines Corporation in the United States, other countries, or both. The IBM logo, PowerPC, PowerPC logo, and PowerPC architecture are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

Linux is a registered trademark of Linus Torvalds. Linux is written and distributed under the GNU General Public License in the United States and other countries.

Other company, product, and service names may be trademarks or service marks of others.

The IBM home page can be found at www.ibm.com.

SysSimPerfAnalysisGuide, Version 3.0

# Contents

| Preface                                                             | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| גערורווווק אטטונצוטרוג וה נהפרוסוא דעוו-געגנפורו גווועומנטר         | . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Performance Modeling with the IBM Full-System Simulator             | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Performance Modeling with SystemSim                                 | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Synergistic Processing Elements (SPEs)                              | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| L1 and L2 Caches.                                                   | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Element Interconnect Bus                                            | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Memory Interface Controller and System Memory                       | . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Enabling the Performance Models in a Simulation                     | . 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| From the Graphical User Interface.                                  | . 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Gathering Performance Metrics                                       | . 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Performance Analysis with Profile Checkpoints and Triggers          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Viewing SPU Performance Statistics                                  | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Capturing Performance Data in a TCL Array                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Enhancing Data Collection with Triggers                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Tutorial: Collecting Performance Data with Checkpoints and Triggers | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Performance Data Collection and Analysis with Emitters              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Emitter Architecture Overview.                                      | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Underlying Emitter Record Data Structure                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Configuring Emitter Event Production                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Specifying Events to Produce Emitter Data                           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Configuring the Number of Emitter Readers.                          | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Starting Emitter Readers                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <i>Tutorial:</i> Configuring Emitter Event Production               | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

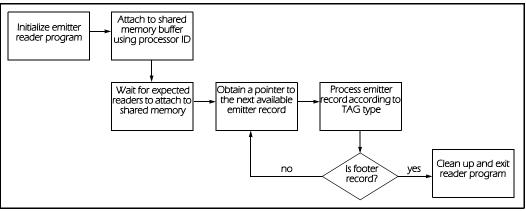

| Developing Emitter Readers to Process Event Data                    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <i>Tutorial:</i> Developing a Basic Emitter Reader                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SPU Performance Statistics                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                     | Performance Simulation and Analysis with the IBM Full-System Simulator         An Overview of the IBM Full-System Simulator         Modeling the CBE Architecture in the IBM Full-System Simulator.         Running Applications in the IBM Full-System Simulator         Performance Modeling with the IBM Full-System Simulator         Performance Modeling with the IBM Full-System Simulator         Performance Modeling with SystemSim         Synergistic Processing Elements (SPEs)         L1 and L2 Caches         Element Interconnect Bus         Memory Interface Controller and System Memory         Enabling the Performance Models in a Simulation         From the Graphical User Interface         From the Gommand Line         Gathering Performance Metrics         Overving SPU Performance Metrics         Capturing Performance Statistics         Capturing Performance Data in a TLL Array         Instrumenting SPU Applications with Performance Profile Checkpoints         Enhancing Data Collection and Analysis with Emitters         Z         Mitter Architecture Overview         Underlying Emitter Event Production         Specifying Events to Produce Emitter Data         Configuring the Number of Emitter Readers         Stating Emitter Readers         Stating Emitter Readers         Stating Emitter Readers to |

# Preface

Analyzing the performance of distributed, real-time, and embedded systems is a challenging task due to the complexity and low-level nature of such systems. The IBM Full System Simulator project (SystemSim) strives to build tools and frameworks that enable software designers to evaluate and visualize the performance of a modeled processor system. With this insight, designers are able to pinpoint bottlenecks in a system and optimize its performance.

The *Performance Analysis Using SystemSim* guide describes the performance analysis methodology and implementation techniques developed to collect and analyze performance metrics for software systems executing on the IBM Full-System simulator.

## **Intended Audience**

This document is intended for designers and programmers who are evaluating the performance of applications and systems software for systems based on the Cell Broadband Engine Architecture (CBEA). Potential users include:

- System and software designers

- Hardware and software tool developers

- Application and product engineers

- Validation engineers

## Using This Version of the Guide

This version of the *Performance Analysis with the IBM Full-System Simulator* applies to version 2.1 of the IBM Full-System Simulator for the Cell Broadband Engine Processor, available from IBM's alphaWorks Emerging Technologies website located at <u>http://www.alphaworks.ibm.com/tech/cellsystemsim</u>.

The guide is organized into topics that cover concepts and procedures for capturing a variety of performance metrics for CBEA applications using performance analysis techniques. This book includes the following chapters and appendices:

- Chapter 1, Performance Simulation and Analysis with the IBM Full-System Simulator, describes the IBM Full System Simulator developed by the IBM Austin Research Lab (ARL), and introduces the Cell Broadband Engine Architecture (CBEA) modeled by the IBM Full-System Simulator.

- Chapter 2, "Performance Modeling with the IBM Full-System Simulator," provides information about performance modeling support in the IBM Full-System Simulator, including descriptions of components for which performance simulation is currently available. It also describes how to enable performance simulation from the simulator command line and graphical user interface.

- Chapter 3, Performance Analysis with Profile Checkpoints and Triggers, describes performance profile checkpoint and trigger functionality, and illustrates how these mechanisms are used to generate application-specified performance data in a simulation.

- Chapter 4, Performance Data Collection and Analysis with Emitters, describes the IBM Full-System Simulation emitter architecture. This section contains a tutorial that describes how to configure the simulator to emit event data, and how to develop emitter readers to analyze the emitted event data. This chapter also describes how to enhance emitter reader functionality with annotations.

- *Appendix A, SPU Performance Statistics,* lists the checkpoint types that were gathered during performance evaluation.

## **Typographical Conventions**

The following typographical components are used for defining special terms and command syntax:

| Convention                        | Description                                                                                                                                                                                                                       |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold typeface                     | Represents literal information, such as:                                                                                                                                                                                          |

|                                   | Information and controls displayed on screen, including menu options, application pages, windows, dialogs, and field names.                                                                                                       |

|                                   | Commands, file names, and directories.                                                                                                                                                                                            |

|                                   | In-line programming elements, such as function names and XML elements when referenced in the main text.                                                                                                                           |

| <i>Italics</i> typeface           | Italics font is used to emphasize new concepts and terms, and to stress important ideas. Additionally, book and chapter titles are displayed in italics.                                                                          |

| Sans serif typeface               | Represents example code output, such as XML output or C/C++ code examples.                                                                                                                                                        |

|                                   | Italic sans serif words or characters in code and commands<br>represent values for variables that you must supply, such as arguments to<br>commands or path names for your particular system. For example:<br>cd /users/your_name |

| (Horizontal or Vertical ellipsis) | In format and syntax descriptions, an ellipsis indicates that some material has been omitted to simplify a discussion.                                                                                                            |

| {} (Braces)                       | Encloses a list from which you must choose an item or information in syntax descriptions.                                                                                                                                         |

| [] (Brackets)                     | Encloses optional items in format and syntax descriptions. For example, in the statement <b>SELECT</b> [DISTINCT], DISTINCT is an optional keyword.                                                                               |

| (Vertical rule)                   | Separates items in a list of choices enclosed in { } (braces) in format and syntax descriptions.                                                                                                                                  |

| UPPERCASE                         | Indicates keys or key combinations that you can use. For example, press<br>CTRL + ALT + DEL.                                                                                                                                      |

| <u>Hyperlink</u>                  | Web-based URIs are displayed in blue text to denote a virtual link to an external document. For example: <u>http://www.ibm.com</u>                                                                                                |

| <b>NOTE</b> This is note text.    | The note block denotes information that emphasizes a concept or provides peripheral information.                                                                                                                                  |

#### Table 1. Typographical Conventions

### **Related Guides and Recommended Reference**

The *IBM Full-System Simulator User's Guide* describes the basic structure and operation of the IBM Full-System Simulator and its graphic user interface (GUI) and command line user interface. The *IBM Full-System Simulator User's Guide* is commonly distributed with alphaWorks releases in the docs directory as **SystemSim.Users.Guide.pdf**.

The IBM Austin Research Lab also recommends the following documentation sources that may provide helpful guidelines and background information about technologies used in the simulation environment:

Practical Programming in Tcl and Tk by Brent B. Welch. Prentice Hall, Inc.

## Contacting the IBM Full-System Simulator Development Team

The IBM Full-System Simulator development team at ARL is very interested in hearing from you about your experience with the IBM Full-System Simulator and its supporting information set. Should you have questions or encounter any issues with the IBM Full-System Simulator, visit the project forum at <a href="http://www.alphaworks.ibm.com/tech/cellsystemsim/forum">http://www.alphaworks.ibm.com/tech/cellsystemsim/forum</a>.

## **CHAPTER 1**

# Performance Simulation and Analysis with the IBM Full-System Simulator

This chapter provides an overview of the IBM Full System Simulator, SystemSim, developed by the IBM Austin Research Lab (ARL), and introduces the Cell Broadband Engine Architecture (CBEA) that is modeled by SystemSim. It also describes configuration parameters for setting up and running the simulation environment in standalone and Linux mode. Topics in this chapter include:

- An Overview of the IBM Full-System Simulator

- Modeling the CBE Architecture in the IBM Full-System Simulator

- Running Applications in the IBM Full-System Simulator

## An Overview of the IBM Full-System Simulator

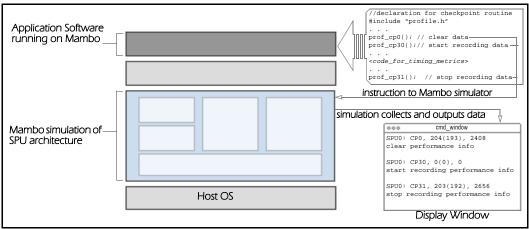

The IBM Full-System Simulator (SystemSim) provides fast but accurate simulation of complete systems with processors that are based on the IBM PowerPC Architecture. SystemSim, originally known by the internal IBM name "Mambo," contains numerous features to support software design and analysis, including parameterized models for architectural features and dynamically selectable model fidelity that enable users to trade simulation accuracy for execution speed. SystemSim has been used extensively inside IBM to support the development of operating systems, compilers, and key software components for new systems well in advance of hardware availability.

The IBM Full-System Simulator is a sophisticated simulation environment that supports both functional and performance simulation of multiple PowerPC cores and a variety of system components. The simulator's processor support includes interrupts, debugging controls, caches, busses, and a large number of architectural features. In addition, The simulator models memory-mapped I/O devices, consoles, disks, and networks that allow operating systems to run in simulation, and boot and run programs.

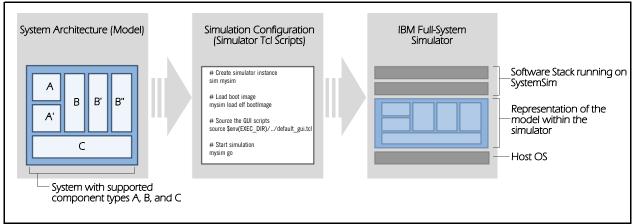

A core advantage of the Full-System Simulator is the level of flexibility that is afforded by its modular, configurable architecture. Each simulation is an instance of the microprocessor architecture it is modeling. Figure 1-1 represents a high-level view of the processor-to-simulation relationship:

Figure 1-1. IBM Full-System Simulator Architecture

As illustrated in the diagram, a system may include any number of supported processor component types, each of which is instantiated in a simulator via custom Tcl configuration scripts. In this manner, a simulation can realistically represent an entire system of equipment, devices, or subsystems, and is able to simulate not only the instructions executed by the processor core, but also its interactions with its surrounding system components.

The IBM Full-System Simulator provides different simulation modes, ranging from functional simulation of processor instructions to performance simulation of an entire system. In most cases, the simulation mode can be changed dynamically at any point in the simulation. However, certain "warm-up" effects may affect the results of performance simulation for some portion of the simulation following a change to cycle mode.

Simple (functional-only) mode models the effects of instructions, without attempting to accurately model the time required to execute the instructions. In simple mode, a fixed latency is assigned to each instruction; the latency can be arbitrarily altered by the user. Since latency is fixed, it does not account for processor implementation and resource conflict effects that cause instruction latencies to vary. Functional-only mode assumes that memory accesses are synchronous and instantaneous. This mode is useful for software development and debugging, when a precise measure of execution time is not required.

- Fast mode is similar to functional-only mode in that it fully models the effects of instructions while making no attempt to accurately model execution time. In addition, fast mode bypasses many of the standard analysis features provided in functional-only mode, such as statistics collection, triggers, and emitter record generation. Fast mode simulation is intended to be used to quickly advance the simulation through uninteresting portions of program execution to a point where detailed analysis is to be performed.

- Cycle (performance) mode: models not only functional accuracy but also timing. It considers internal execution

and timing policies as well as the mechanisms of system components, such as arbiters, queues, and pipelines.

Operations may take several cycles to complete, accounting for both processing time and resource constraints.

These simulation modes are used to support concurrent development and performance evaluation of a number of software and hardware systems. The primary objective of this focus is to enable internal teams and IBM partners to:

- Use the simulator to gather and compare performance data with a greater level of fidelity.

- Characterize the workload on the system.

- Forecast performance at future loads and fine-tune performance benchmarks for future validation.

The IBM Full-System Simulator also includes trace collection and debugging interfaces to allow detailed analysis of the simulated hardware and software.

## Modeling the CBE Architecture in the IBM Full-System Simulator

In 2001, Sony, Toshiba, and IBM (STI) combined research and development efforts to create an advanced Cell Broadband Engine Processor (CBEP) for a new wave of devices in the emerging broadband era. Shortly after project inception, STI engaged the IBM Austin Research Laboratory (ARL) to model the Cell Broadband Engine processor to support software simulation and performance testing using the IBM Full-System Simulator.

Initially, the IBM Full-System Simulator Cell model supported functional simulation of the PPE and SPU processors. The ARL development team incorporated a standalone simulator for SPU programs (called *apusim*) into the simulator to provide SPU simulation functionality. The apusim simulator was developed by the STI Design Center and supported both functional and performance simulation of standalone SPU programs. In the IBM Full-System Simulator, SPU program execution can be performed in either instruction mode, which performs functional simulation only, or pipeline mode, which performs functional and performance and performance simulation. In pipeline mode, the behavior of the SPU execution pipeline is modeled in detail and statistics on pipeline operation are collected. However, SPU instructions that interact with other parts of the system, such as the MFC channels or DMA operations, are only modeled at the functional level.

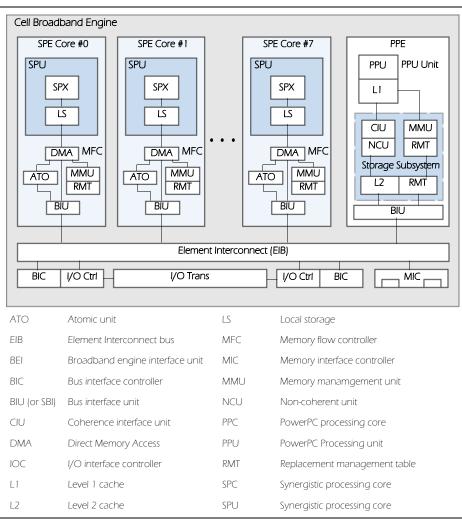

Figure 1-2. High-Level Block Diagram of the Simulated CBEA

## **Running Applications in the IBM Full-System Simulator**

A key attribute of the IBM Full-System Simulator is its ability to boot and run a complete PowerPC system. By booting an operating system, such as Linux, the simulator can execute many typical application programs that utilize standard operating system functionality. When Linux is booted in the simulator, the Linux operating system (running in the simulated environment) loads the application and is responsible for all operating system calls.

Alternatively, applications can be run in *standalone* mode, in which all operating system functions are supplied by the simulator and normal operating system effects do not occur, such as paging and scheduling. In standalone mode, the simulator simply loads the application into simulated memory and begins the simulation at the application's entry point. The simulator can also execute SPU programs in standalone mode on a given SPU. This mode provides information that is more directly a result of the intrinsic program design and implementation. This is useful for application's performance measurement and analysis.

The *IBM Full-System Simulator User's Guide* describes the commonly used commands to create full-system or standalone simulation environments.

## **CHAPTER 2**

# Performance Modeling with the IBM Full-System Simulator

This chapter provides information about performance modeling support in the IBM Full-System Simulator, including descriptions of components for which performance simulation is currently available. It also describes how to enable performance simulation from the simulator command line and graphical user interface. Topics in this chapter include:

- Performance Modeling with SystemSim

- Enabling the Performance Models in a Simulation

- Gathering Performance Metrics

## Performance Modeling with SystemSim

Support for performance simulation has been evolving since the IBM Full-System Simulator for the Cell Broadband Engine platform was originally released on alphaWorks. The first version of the simulator provided a cycle-accurate model of the SPU interactions, which enabled developers to gather detailed performance data about the execution of SPU programs, such as pipeline stalls, operand dependencies, and so forth. Subsequent versions of the simulator have provided performance simulation of memory subsystem functions (in version 2.0) and the PPU execution (in version 2.1). As a result, the simulator now supports performance simulation for nearly all aspects of the Cell Broadband Engine processor operation.

It is important to note that the simulator provides significant timing information about processor components, and has proven very useful in exploring the functionality and performance of Cell/B.E. based processor systems. However, running on hardware provides the most definitive performance results, and should be used when precise performance information is needed.

#### Synergistic Processing Elements (SPEs)

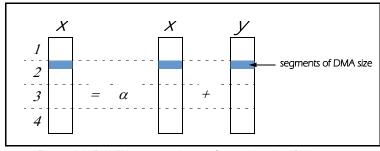

Systemsim accurately models the microarchitectural flow of instructions through the SPU pipelines, including instruction prefetch logic, branch hint and mispredict behaviors, issue stall conditions, execution latencies, and resource contention. The SPU pipeline model includes extensive instrumentation to provide performance metrics and cycle-level tracing. The MFC performance model includes bus interface unit queues and policies, DMA engine queues and state machines, address translation engine behaviors, and the atomic cache. SystemSim's MFC model unrolls DMA single and list commands into their individual transaction components. These are processed by the various state machine engines, collect in queues, and flow across interconnects in order to capture the latency and bandwidth effects of arbitration policies, queue management, and resource contention.

#### L1 and L2 Caches

Since cache utilization can play a significant role in system and application performance, the simulator provides the ability to accurately model and measure the performance of a cache subsystem. The simulator cache models for the L1 and L2 caches provide performance metrics that are useful in analyzing PPE performance. The L1 and L2 caches are accurately modeled in terms of size, associativity, replacement policies, and latency. Currently the cache models do not support the Replacement Management Table (RMT) features of the CBE architecture.

#### **Element Interconnect Bus**

The Element Interconnect Bus (EIB) model handles the complex rules for managing data coherence as specified in the Broadband Interface Protocol (BIF), including command formats, transaction types, and the snooper cache coherence protocol for the CELL processor system. Rather than using a simplistic "method call or function call-back" approach, the simulator models the flow of bus transactions. including out-of-order transaction support, split transaction designs, arbitration policies, fragmenting (scatter/gather), and flow control. This design enables transactions to be tracked accurately through the data analysis framework.

#### Memory Interface Controller and System Memory

The Memory Interface Controller (MIC) model connects the EIB to the off-chip system memory and manages the flow of data onto and off of the Cell Broadband Engine processor from system memory. The MIC model also supports scheduling policies between the read queue and write queue in order to minimize latency and implements a snoop-based cache coherence.

The simulator currently does not provide a model for RAMBUS architecture memory; instead it contains a performance model for DDR2 SDRAM memory that is configured to approximate the performance of the RAMBUS XDR memory used by the Cell processor.

## **Enabling the Performance Models in a Simulation**

The performance models described above can be enabled from the GUI using the performance models dialog or with simulator commands. The performance models can be enabled at any time after the simulated machine has been defined, but typically are not enabled until after the operating system has been booted. To enable the performance models in a simulation, complete the following steps:

#### From the Graphical User Interface

To enable the performance models from the graphical user interface:

1. Click the **Mode** button on the main GUI window.

|                        | sys                  | stemsim-cell       |                    |                   |

|------------------------|----------------------|--------------------|--------------------|-------------------|

| ile Window             |                      |                    |                    | Ht                |

| ∃- 📮 mysim 🛛 🔼         |                      | сри                | ✓ Cycles: 9,282,77 | 7                 |

| 🖻 🗀 BE_0               |                      |                    |                    | 1                 |

| ⊕ 📄 PPE0:0:0           | Advance Cycle Am     | ount : 1           |                    |                   |

| PPE0:0:1     SPE0      | Advance Cycle        | Go                 | Stop               | Service GDB       |

| B SPE1                 | Triggers/Breakpoints | Update GUI         | Debug Controls     | Options           |

| B- C SPE2              | Emitters             | Mode               | SPU Modes          | SPE Visualization |

|                        | Process-Tree         | Process-Tree-Stats | Track All PCs      | Event Log         |

| B SPE5                 |                      |                    |                    | Exit              |

| 🗉 🗀 SPE6               |                      |                    |                    |                   |

| 🕮 🧰 SPE7               |                      |                    |                    |                   |

| - Load-Elf-App         |                      |                    |                    |                   |

| Load-Elf-Kernel        |                      |                    |                    |                   |

| ₽ 📮 BE_1               |                      |                    |                    |                   |

| PPE1:0:0               |                      |                    |                    |                   |

| PPE1:0:1               |                      |                    |                    |                   |

| 🖽 🗀 SPEO               |                      |                    |                    |                   |

| 🗉 🗀 SPE1               |                      |                    |                    |                   |

| 😐 🗀 SPE2               |                      |                    |                    |                   |

| 😐 🗀 SPE3               |                      |                    |                    |                   |

| 🗉 🗀 SPE4 🗤             |                      |                    |                    |                   |

| Running Stalled Halted |                      |                    |                    |                   |

Figure 2-1. SystemSim Cell Graphical User Interface

2. SystemSim displays the simmodes window containing a message indicating the current simulation mode and three buttons which will change the simulation mode to fast, simple, or cycle mode. Figure 2-2 shows an example of this dialog window. This dialog provides a convenient way to set the simulation mode for components of the system in a consistent manner. The simulation mode can also be selected with the "mysim mode" command and displayed with the "mysim display mode" command.

|           | simmode                   |            |

|-----------|---------------------------|------------|

| S         | imulator is in mode SIMPL | .E         |

| Fast Mode | Simple Mode               | Cycle Mode |

Figure 2-2. Simulation Mode Window

3. The simulator also provides the SPU Modes dialog to set each SPU's simulation mode to instruction mode, pipeline (cycle accurate) mode or fast mode. The SPU Modes dialog, shown in Figure 2-3, is accessed from the

**SPU Modes** button on the main GUI window. If the simulator is launched in SMP mode, this dialog will show all the SPUs in both BEs; otherwise only the SPUs for BE 0 are displayed.

| 🗙 spumodes0 📃 🗖 🗙                 |

|-----------------------------------|

| SPU0: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU1: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU2: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU3: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU4: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU5: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU6: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| SPU7: 🔷 Pipe 🔶 Instruction 🕹 Fast |

| All BE:0 Pipe Instruction Fast    |

| Refresh                           |

Figure 2-3. SystemSim SPU Modes

- a. For each individual SPU, click the level of timing mode to simulate: **Pipe**, **Instruction**, or **Fast**. The SPU mode for an individual SPU can also be selected using the Model toggle menu sub-item under each SPE in the tree menu at the left of the main control panel.

- b. To enable the same timing mode for all SPUs in the BE, click the corresponding button.

- c. Click **Refresh** to synchronize the window with any changes to the modeling mode that may have been updated by the command line interface or the tree view.

- 4. Click Go in the main GUI window to start the simulation with performance models enabled.

#### From the Command Line

To enable all performance models from the command line, type the following command:

turn\_perf\_models\_on

## **Gathering Performance Metrics**

The simulator provides an extensive variety of data collection and analysis capabilities, including the following mechanisms:

- Performance Profiling Checkpoints. Performance profile checkpoints provide the most basic level of code instrumentation for gaining insight into SPU performance. The simulator provides a set of checkpoint instructions that can be added to a region of code to control the collection and display of SPU performance data. These instructions offer a very lightweight, minimally intrusive mechanism for the user to obtain performance information for SPU program execution. See Chapter 3, "Performance Analysis with Profile Checkpoints and Triggers," for information and instructions for adding performance profile checkpoints to application code.

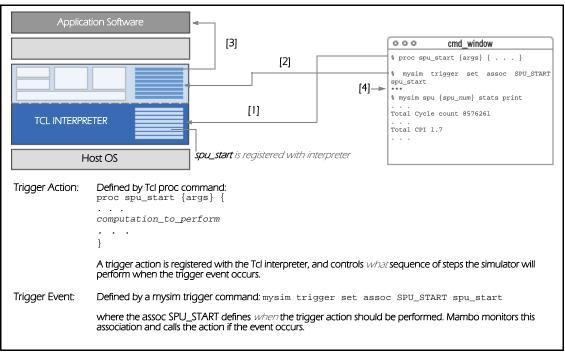

- Triggers. Triggers can be used to invoke user-supplied TCL procedures to collect and aggregate performance data when specific types of simulation events occur. This general-purpose mechanism can be used to implement a variety of breakpoints, accumulate metrics, produce messages, or perform any number of tasks that are supported in a TCL procedure. The simulator provides trigger events for the program counter, memory accesses, cycle counts, console output strings, and a number of simulation events. See Chapter 3, "Performance Analysis with Profile Checkpoints and Triggers," for information and instructions for adding triggers to application code.

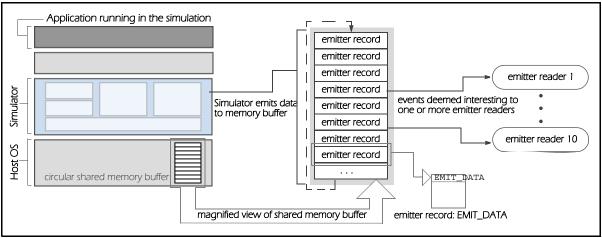

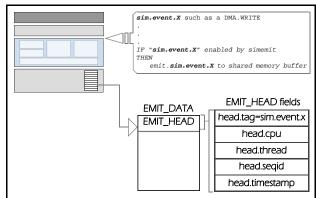

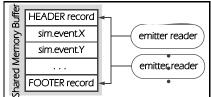

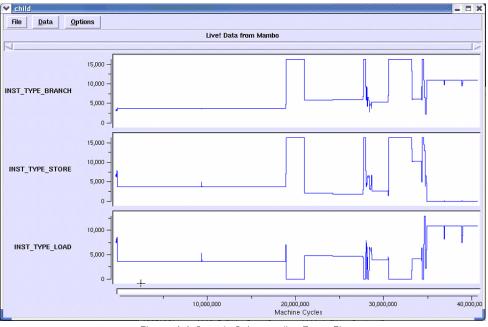

- Emitters. The emitter framework is a user-extensible and customizable analysis framework that enables detailed data collection for performance analysis, basic data visualization, and trace generation. Users can write emitter